| การแปลงการแยกส่วนต่างภายใน |  |

| ความละเอียด: 16 บิต | |

| เอาต์พุตสลักสามสถานะ | |

| ติดตามอย่างต่อเนื่องระหว่างการถ่ายโอนข้อมูล | |

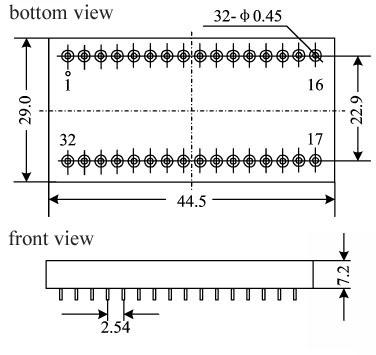

| แพ็คเกจโลหะ 32 สาย |

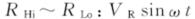

HSDC/HRDC1746 ซีรีส์ซิงโคร/ตัวแก้ไขไปยังตัวแปลงดิจิทัลได้รับการออกแบบ | บนหลักการของหลักการติดตามเซอร์โวประเภท II และใช้ | |||||

อินพุตการแยกส่วนต่าง, เอาต์พุตข้อมูลใช้สลักสามสถานะ | โหมดเหมาะสำหรับการแปลงสัญญาณแอนะล็อก/ดิจิตอลของ | ซิงโครไนซ์สามสายและตัวแก้ไขสี่สาย ด้วยความเร็วในการแปลงที่รวดเร็ว | และประสิทธิภาพที่เสถียรและเชื่อถือได้ อุปกรณ์นี้สามารถใช้ได้อย่างกว้างขวาง ในการวัดมุมและระบบควบคุมอัตโนมัติ | ผลิตภัณฑ์นี้ทำขึ้นโดยกระบวนการผสมฟิล์มหนาแบบไฮบริดและเป็น | ||

แพ็คเกจโลหะที่ปิดสนิท DIP 32 สาย ทั้งดีไซน์และ | ||||||

การผลิตผลิตภัณฑ์เป็นไปตามข้อกำหนดของ GJB2438A-2002 | “ข้อกำหนดทั่วไปสำหรับวงจรรวมไฮบริด” และเฉพาะ | ข้อมูลจำเพาะของผลิตภัณฑ์ | ||||

4. ประสิทธิภาพทางไฟฟ้า (ตารางที่ 2 ตารางที่ 3) | Synchro to Digital Converters หรือ Resolver to Digital Converters (HSDC/HRDC1746 Series) | ตารางที่ 2 เงื่อนไขการจัดอันดับและเงื่อนไขการใช้งานที่แนะนำ | ตารางที่ 3 ลักษณะทางไฟฟ้า | สูงสุดแน่นอน ค่านิยม | ||

แรงดันไฟจ่าย Vs: ± 17.25VDC | พารามิเตอร์ | -3 | 3 | |||

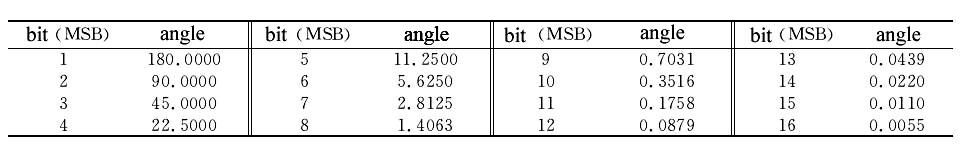

HSDC/HRDC | 1746 ซีรีส์ | 16 | ||||

หมายเหตุ | แรงดันไฟจ่ายลอจิก VL: +7V | 50 | ช่วงอุณหภูมิในการจัดเก็บ: -55 ℃ ~ 150 ℃ | |||

นาที. | แม็กซ์ | 2 | 90 | |||

เงื่อนไขการใช้งานที่แนะนำ | แรงดันไฟจ่าย Vs: ±15± 5% | 2 | ความแม่นยำ/นาทีเชิงมุม | |||

| 2.6k |  |

| การเปลี่ยนเฟสระหว่างสัญญาณและการกระตุ้น:<±10% แรงดันสัญญาณ (ค่าที่มีประสิทธิภาพ)/V ช่วงอุณหภูมิในการทำงาน (TA): -40~+105℃  | |

| แรงดันอ้างอิง (ค่าประสิทธิผล)/V | 115 |

| |

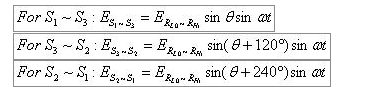

| ได้รับฟังก์ชันข้อผิดพลาด: |

ผ่านการขยายข้อผิดพลาด การเลือกปฏิบัติเฟส และการกรองสิ่งนี้of ฟังก์ชันข้อผิดพลาด ได้รับ sin(θ-φ) เมื่อ θ-φu003d0 (อยู่ในความแม่นยำ | ของตัวแปลง) ข้อผิดพลาดนี้จะทำให้แรงดันไฟฟ้าควบคุมofออสซิลเลเตอร์เอาท์พุตการแก้ไขพัลส์เพื่อเปลี่ยนมุมดิจิตอลไบนารี φ |

| |

| ของตัวนับย้อนกลับเพื่อให้ค่าเอาต์พุต φ เท่ากับ | อินพุต θ ภายในความแม่นยำของตัวแปลง ระบบจะเสถียร |

| และสามารถติดตามการเปลี่ยนแปลงของมุมอินพุต φ ด้วยวิธีนี้ ไบนารีดิจิตอล | |

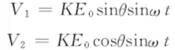

ตัวนับย้อนกลับ (รูปที่ 2) | มะเดื่อ 2 แผนภาพวงจรบล็อก | (1) ลักษณะไดนามิก | ฟังก์ชั่นการถ่ายโอนของตัวแปลงแสดงในรูปที่ 3: | กำไรจากวงเปิด: | ฟังก์ชันวงปิด: |

1 | NC | สำหรับโมดูลของรุ่นนี้ Kau003d48000/S2, T1u003d7.1ms, T2u003d1.25ms | 17 | NC | รูปที่ 3 การถ่ายโอนฟังก์ชันของตัวแปลง |

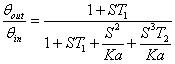

2 | D9 | (2)วิธีการถ่ายโอนข้อมูลและลำดับเวลา | 18 | การควบคุมการเลือกชิป เปิดใช้งาน | พินนี้เป็นพินอินพุทของลอจิกควบคุม หน้าที่ของมันคือเอาท์พุท |

3 | ข้อมูลไปยังตัวแปลงเพื่อให้เกิดการควบคุมสามสถานะ ระดับต่ำคือ | ถูกต้อง ข้อมูลเอาท์พุตของตัวแปลงใช้บัสข้อมูล เมื่ออยู่ที่ | 19 | ระดับสูง, พินเอาต์พุตข้อมูลของตัวแปลงอยู่ในสามสถานะ, the | อุปกรณ์ไม่ได้ใช้รถบัส |

4 | เลือกไบต์ | พินนี้เป็นพินอินพุตควบคุม หน้าที่ของมันคือการดำเนินการจากภายนอก | 20 | การควบคุมการเลือกข้อมูลเอาต์พุตของตัวแปลงในการถ่ายโอน | โหมดบัสข้อมูล 8 บิตหรือบัสข้อมูล 16 บิต เมื่อถ่ายโอนบัสข้อมูล 16 บิต |

5 | ต้องใช้โหมด ให้ขาลอจิกนี้สูง ข้อมูลจะเป็น | ถ่ายโอนในบัสเอาต์พุตไบต์สูงอยู่ในพิน D1 ถึง D8 (D1 is | 21 | บิตสูง) และไบต์ต่ำอยู่ใน D9 ถึง D16 เมื่อโอนบัสข้อมูล 8 บิต | ต้องการโหมดข้อมูลจะได้รับในพิน D1 ถึง D8 (จัดเรียงจากสูง |

6 | ถึงต่ำ) และสูง 8 บิตและ 8 บิตต่ำจะได้รับสองครั้ง | ลำดับ กล่าวอีกนัยหนึ่ง เมื่อ Byte select เป็นตรรกะสูง สูง 8 บิต | 22 | เป็นเอาต์พุตและเมื่อลอจิกต่ำจะมีเอาต์พุต 8 บิตต่ำ | การควบคุมการล็อกข้อมูล (สัญญาณยับยั้ง ) ยับยั้ง |

7 | พินนี้เป็นพินอินพุทของลอจิกควบคุม หน้าที่ของมันคือเอาท์พุท | ข้อมูลภายนอกไปยังตัวแปลงเพื่อให้ทราบถึงการล็อคหรือบายพาสเสริม | 23 | ควบคุม. ที่ระดับสูง ข้อมูลเอาท์พุตของตัวแปลงโดยตรง | เอาต์พุตโดยไม่ต้องสลัก ดูแผนภาพลำดับเวลาของข้อมูล |

8 | โอนย้าย. ที่ระดับต่ำ ข้อมูลเอาท์พุตของคอนเวอร์เตอร์จะถูกล็อค | การวนซ้ำภายในจะไม่ถูกขัดจังหวะ และการติดตามยังคงทำงานทั้งหมด | 24 | D1 | เวลา แต่ตัวนับไม่แสดงผลข้อมูล เมื่อจำเป็นต้องโอน |

9 | ข้อมูล ตัวแปลงแรกจะทำให้สัญญาณควบคุม Inhibit ล็อคข้อมูลจากสูงไปต่ำ ทำให้ตรรกะต่ำสำหรับ 640ns จากนั้นตั้งค่า Enable input เป็นต่ำ (ในขณะนี้อุปกรณ์ใช้ data bus) จากนั้น | รับข้อมูลผ่านการเลือก Byte จากนั้นเปลี่ยนตรรกะการควบคุมทั้งหมดให้สูง | 25 | D2 | เพื่อรีเฟรชและล็อคข้อมูลเพื่อเตรียมพร้อมสำหรับการถ่ายโอน |

10 | ข้อมูลถัดไป โปรดดูแผนภาพลำดับเวลาของการถ่ายโอนข้อมูล Fig.4 | และรูปที่ 5 | 26 | D3 | (3)วิธีการลดทอนสัญญาณอินพุต (รูปที่ 4 และรูปที่ 5) |

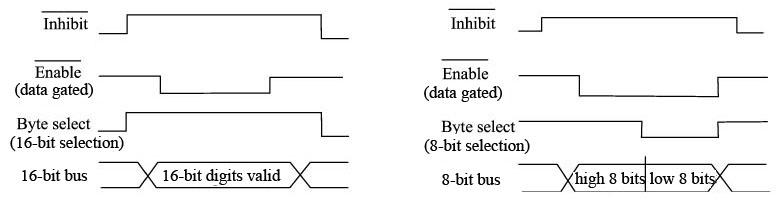

11 | รูปที่ 4 ลำดับเวลาของการถ่ายโอนบัส 16 บิต | รูปที่ 5 ลำดับเวลาของการถ่ายโอนบัส 8 บิต | 27 | D4 | 6. เส้นโค้ง MTBF (รูปที่ 6) |

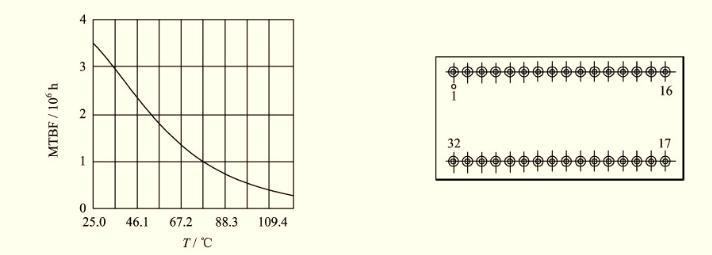

12 | Synchro to Digital Converters หรือ Resolver to Digital Converters (HSDC/HRDC1746 Series) | 7. การกำหนดพิน (รูปที่ 7 ตารางที่ 4) | 28 | D5 | Synchro to Digital Converters หรือ Resolver to Digital Converters (HSDC/HRDC1746 Series) |

13 | S3 | รูปที่ 6 กราฟอุณหภูมิ MTBF | 29 | D6 | รูปที่ 7 การกำหนดพิน (มุมมองด้านล่าง) |

14 | S2 | (หมายเหตุ: ตาม GJB/Z299B-98 คาดว่าสภาพดี) | 30 | D7 | ตารางที่ 4 คำอธิบายการใช้งานของขั้วต่อลีด |

15 | S1 | เข็มหมุด | 31 | D7 | สัญลักษณ์ |

16 | NC | ความหมาย | 32 | NC | เข็มหมุด |

พื้น | D12 | เอาต์พุตดิจิตอลสำหรับ 12thbit | -VS | -15V แหล่งจ่ายไฟ | D13 | เอาต์พุตดิจิตอลสำหรับ 13thbit | + VS | แหล่งจ่ายไฟ 15V |

D14 | เอาต์พุตดิจิตอลสำหรับ 14thbit | Ni | ยับยั้ง | Ni | การควบคุมการล็อคข้อมูล | D15 | เอาต์พุตดิจิตอลสำหรับ 15thbit |

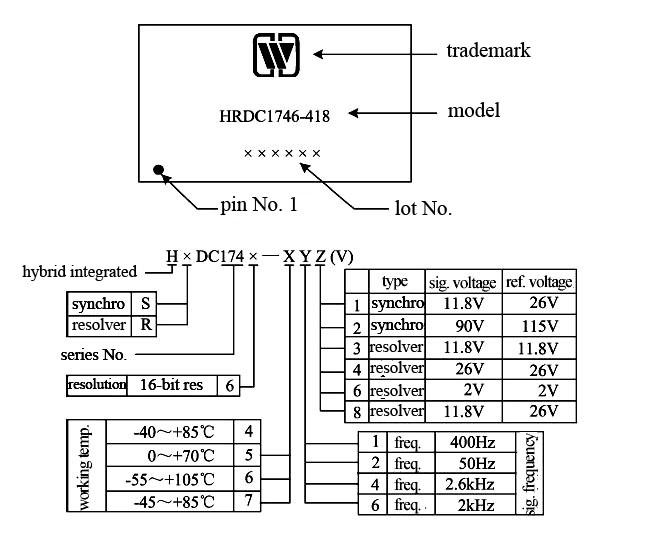

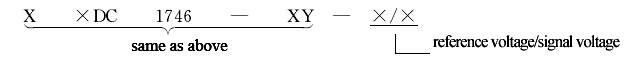

X

X