| การแปลงการแยกส่วนต่างภายใน |  |

| ความละเอียด 16 บิต | |

| ความแม่นยำ: 2 นาทีเชิงมุม | |

| เอาต์พุตสลักสามสถานะ | |

| ความเร็วในการติดตามอย่างต่อเนื่องสูง | |

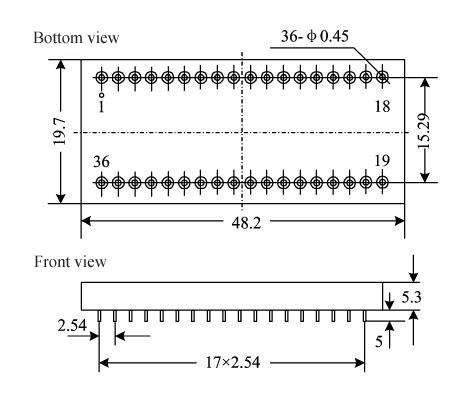

| แพ็คเกจ DDIP ปิดผนึกด้วยโลหะป้องกันหมอกเกลือ 36 สาย | |

| พินทูพินเข้ากันได้กับรุ่น SDC14560 ของบริษัท DDC |

| อุปกรณ์แปลงรวมสำหรับการติดตามอย่างต่อเนื่องที่ออกแบบบน | หลักการของเซอร์โวรุ่น II ผลิตภัณฑ์ชุดนี้ได้รับการออกแบบและ |

| ผลิตโดยกระบวนการ MCM องค์ประกอบหลักใช้ชิปพิเศษ | |

| พัฒนาอย่างอิสระโดยสถาบันของเรา การจัดเรียงพินคือ | |

| เข้ากันได้กับผลิตภัณฑ์ซีรีส์ SDC14560 ของบริษัท American DDC, 16 บิต | |

| เอาต์พุตสลักข้อมูลรหัสไบนารีธรรมชาติแบบขนาน 36 บรรทัด DIP ทั้งหมด | |

| แพคเกจโลหะปิดผนึกมีข้อดีของความแม่นยำสูงขนาดเล็ก | |

| ปริมาณ, การใช้พลังงานต่ำ, น้ำหนักเบาและความน่าเชื่อถือสูงเป็นต้น, | และสามารถใช้กันอย่างแพร่หลายในอาวุธยุทธศาสตร์และยุทธวิธีที่สำคัญเช่น |

| เครื่องบิน, เรือเดินทะเล, ปืนใหญ่, ขีปนาวุธ, เรดาร์, รถถัง ฯลฯ | |

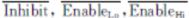

| 4. ประสิทธิภาพไฟฟ้า (ตารางที่ 1 ตารางที่ 2) | |

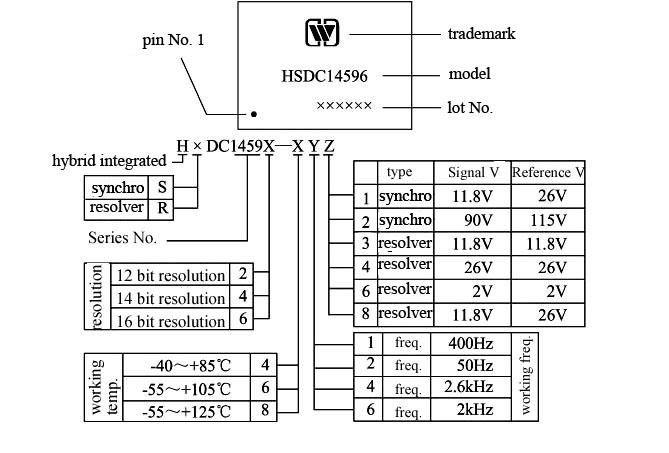

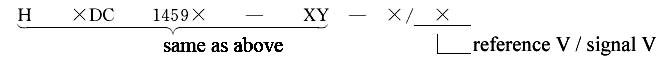

| Synchro to Digital Converters หรือ Resolver to Digital Converters (HSDC/HRDC1459 Series) | |

| ตารางที่ 1 เงื่อนไขการจัดอันดับและเงื่อนไขการใช้งานที่แนะนำ | |

| ค่าสัมบูรณ์ สูงสุด ค่านิยม |

| แรงดันสัญญาณ V1: ค่าพิกัด ±20% | แรงดันอ้างอิง VRef: ค่าพิกัด ±20% | ความถี่ในการทำงาน f: ค่าพิกัด ±20% | |

| อุณหภูมิการจัดเก็บ Tstg: -65~150℃ | เงื่อนไขการใช้งานที่แนะนำ | ||

| แรงดันไฟจ่ายแบบลอจิก VL: 5±0.5V | แรงดันไฟจ่าย Vs: 15 ± 0.75V | ||

| แรงดันสัญญาณ V1: ค่าพิกัด ±10% | แรงดันอ้างอิง VRef: ค่าพิกัด ±20% | ความถี่ในการทำงาน f: ค่าพิกัด ±20% | — |

| ช่วงอุณหภูมิในการทำงาน (TA): -55 ℃ ~ 125 ℃ | หมายเหตุ: * แสดงว่าสามารถปรับแต่งได้ตามความต้องการของผู้ใช้ | ตารางที่ 2 ลักษณะทางไฟฟ้า | พารามิเตอร์ |

| เงื่อนไข | — | HSDC14569 ซีรีส์ | (VSu003d15V, VLu003d+5V) |

| มาตรฐานทางทหาร (Q/HW20725-2006) | — | 2V | นาที. |

| แม็กซ์ | — | ปณิธาน | ระบบไบนารี รหัสดิจิทัลแบบคู่ขนาน |

| 16 บิต | — | 2V | ความแม่นยำ |

| ± 10% ของแรงดันสัญญาณ แรงดันอ้างอิง และช่วงผันผวนของความถี่ในการทำงาน | — | -2 นาทีเชิงมุม | +2 นาทีเชิงมุม |

| ช่วงความถี่อ้างอิง | — | 50Hz | 2600Hz |

| ช่วงของแรงดันอ้างอิง | — | 115V | อิมพีแดนซ์อินพุตอ้างอิง |

4.4kΩ 4.4kΩ | — | 0 | 129.2 kΩ |

ช่วงของแรงดันสัญญาณ ช่วงของแรงดันสัญญาณ | — | 0 | 90V |

สัญญาณอินพุตอิมพีแดนซ์ สัญญาณอินพุตอิมพีแดนซ์ | — | 0 | 4.4kΩ |

| 102.2 kΩ | — | การเปลี่ยนเฟสสัญญาณ/อ้างอิง | —70° |

| +70° | — | อินพุตลอจิกระดับ | ลอจิก “1” ≥3.3V |

| ลอจิก “0” ≤0.8V | — | ป้อนข้อมูล | 0.8V |

| ป้อนข้อมูล | — | 0.8V | |

| ป้อนข้อมูล | — | — | 0.8V |

| ระดับตรรกะเอาต์พุต | — | — | ลอจิก “1” ≥3.3V |

| ลอจิก “0” ≤0.8V | — | — | เอาต์พุตโค้ดมุมดิจิทัล |

| ลอจิก “1” ≥3.3V | — | — | ลอจิก “0” ≤0.8V |

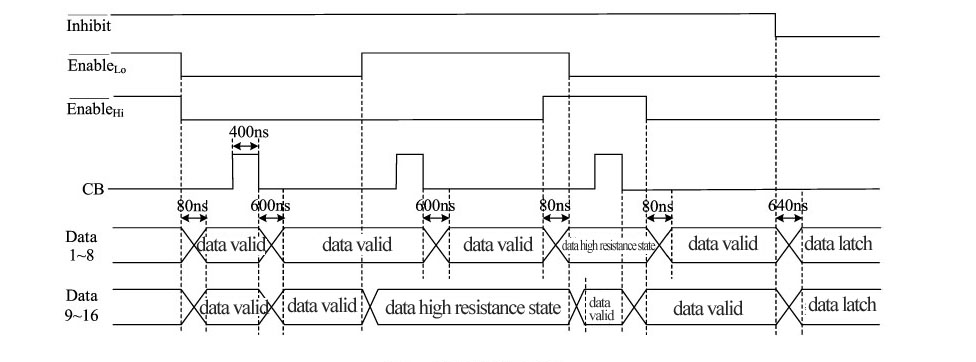

| การแปลงสัญญาณไม่ว่าง (CB) เอาท์พุต | — | 200ns | 600ns |

| การตรวจจับข้อผิดพลาดบิตเอาต์พุต | ลอจิก “0” แสดงว่ามีข้อผิดพลาด | — | กำลังโหลด |

| 3TTL | ติดตามความเร็ว | ||

| 2.5rps | อัตราเร่งคงที่ | ||

| +10V ปัจจุบัน VSu003d+15V 10mA |  VS u003d—15V |

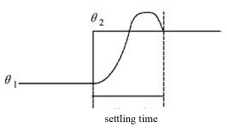

ความเร็ว. กระบวนการสั่นของมุมดิจิตอลเอาท์พุตแสดงใน

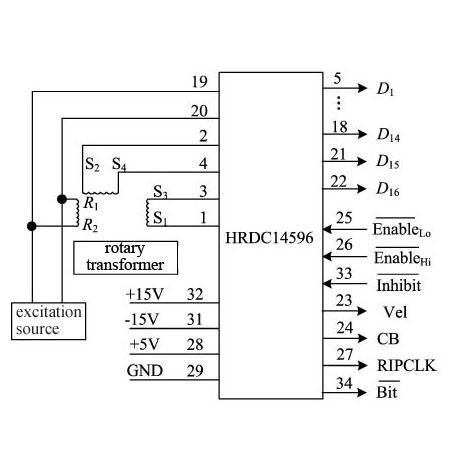

ความเร็ว. กระบวนการสั่นของมุมดิจิตอลเอาท์พุตแสดงใน 6. หลักการทำงาน (รูปที่ 3)

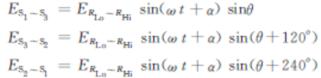

6. หลักการทำงาน (รูปที่ 3)| Synchro to Digital Converters หรือ Resolver to Digital Converters (HSDC/HRDC1459 Series) สัญญาณอินพุตของการซิงโครไนซ์ (หรือตัวแก้ไข) จะถูกแปลงเป็นสัญญาณมุมฉากผ่านการแยกส่วนต่างภายใน: | |

Vcosu003dKE0sin (ωt+α) cosθ (cos)ofโดยที่ θ คือมุมอินพุตแบบอะนาล็อก รูปที่ 2 เส้นโค้งของการตอบสนองขั้นตอน | สัญญาณทั้งสองนี้และมุมดิจิตอล φ ของตัวนับย้อนกลับภายในof คูณด้วยตัวคูณของฟังก์ชันไซน์และโคไซน์และ are รักษาข้อผิดพลาด: |

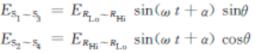

| การขยายเสียง การเลือกปฏิบัติเฟสและการกรองแบบบูรณาการ if | θ-φ≠0, ออสซิลเลเตอร์ที่ควบคุมด้วยแรงดันไฟฟ้าจะส่งสัญญาณพัลส์และ | การนับตัวนับที่ย้อนกลับได้ จนกระทั่ง θ-φ กลายเป็นศูนย์ภายในความแม่นยำของ | ตัวแปลงระหว่างกระบวนการนี้ การแปลงจะติดตามการเปลี่ยนแปลงของ | มุมอินพุตตลอดเวลา | วิธีการอ่าน: |

| 1 | S1 | มีสองวิธีต่อไปนี้สำหรับการถ่ายโอนข้อมูล: | 25 |  | (1) วิธียับยั้ง: |

| 2 | S2 | หลังจาก 640ns ของ | 26 |  | ตรรกะต่ำ ข้อมูลเอาท์พุตถูกต้อง และตัวแปลงตระหนักถึงการถ่ายโอนข้อมูลผ่าน |

| 3 | S3 | และ | 27 | . หลังจากปล่อย Inhibit ระบบจะสร้างพัลส์ที่มีความกว้างเท่ากับพัลส์ที่ไม่ว่างสำหรับการอัปเดตข้อมูลโดยอัตโนมัติ | (2) โหมดหน้าอก: |

| 4 | S4 | ที่ขอบที่เพิ่มขึ้นของพัลส์ว่าง ตัวนับแบบย้อนกลับได้สามสถานะจะนับ ที่ขอบจากมากไปน้อยของพัลส์ว่าง มันจะสร้างชีพจรสลักภายในที่มีความกว้างเท่ากับพัลส์ไม่ว่างสำหรับการอัปเดตข้อมูลของสลักสามสถานะ ลำดับเวลาของการถ่ายโอนข้อมูลจะแสดงในรูปที่ 600 ในรูปอื่น ๆ ใน จากตรรกะไม่ว่างต่ำ การถ่ายโอนข้อมูลที่เสถียรนั้นถูกต้อง ในโหมดการอ่านแบบอะซิงโครนัส เอาต์พุตไม่ว่างคือพัลส์เทรนระดับ CMOS ความกว้างของระดับสูงและต่ำขึ้นอยู่กับความถี่ในการทำงานและความเร็วในการหมุนของอุปกรณ์ที่เลือก | 28 | VL | รูปที่ 4 ลำดับเวลาของการถ่ายโอนข้อมูล |

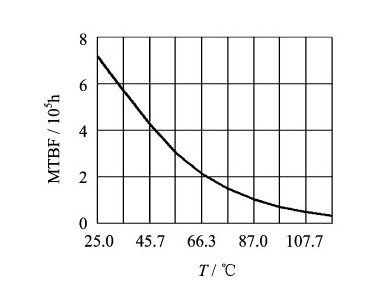

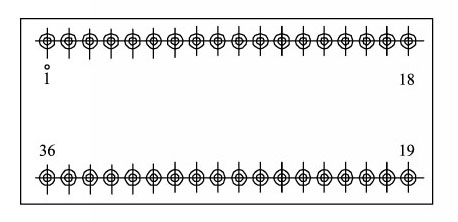

| 7. MTBF เส้นโค้ง (รูปที่ 5) | Synchro to Digital Converters หรือ Resolver to Digital Converters (HSDC/HRDC1459 Series) | รูปที่ 5 เส้นโค้งอุณหภูมิ MTBF | 29 | 8. การกำหนดพิน (รูปที่ 6, ตาราง 3) | Synchro to Digital Converters หรือ Resolver to Digital Converters (HSDC/HRDC1459 Series) |

| 19 | รูปที่ 6 การกำหนดพิน (มุมมองด้านล่าง) | (หมายเหตุ: ตาม GJB/Z299B-98 คาดว่าสภาพพื้นดี) | 30 | NC | ตารางที่ 3 การกำหนดพิน |

| 20 | RL | เข็มหมุด | 31 | สัญลักษณ์ | ความหมาย |

| 21 | เข็มหมุด | สัญลักษณ์ | 32 | VS | ความหมาย |

| 22 | อินพุตตัวแก้ไข S1 (หรือ อินพุตซิงโครไนซ์ S1) | การควบคุมแบบดิจิตอลที่เปิดใช้งาน 8 บิตที่ต่ำกว่า | 33 | อินพุตตัวแก้ไข S2 (หรือ อินพุตซิงโครไนซ์ S2) | การควบคุมแบบดิจิทัลที่เปิดใช้งาน 8 บิตที่สูงขึ้น |

| 23 | อินพุตตัวแก้ไข S3 (หรือ อินพุตซิงโครไนซ์ S3) | RIPCLK | 34 | เอาต์พุตสัญญาณซีโร่บิต | อินพุตตัวแก้ไข S4 (ปล่อยไว้โดยไม่เชื่อมต่อ) |

| 24 | CB | +5V แหล่งจ่ายไฟ | 5月18日 | NC | D1-D14 |

| ดิจิตอลเอาท์พุต 1(MSB)-14 | GND |

| พื้น | RHi |

| อินพุตสัญญาณอ้างอิงระดับสูง | ไม่มีการเชื่อมต่อ |

| RL | อินพุตสัญญาณอ้างอิงต่ำสุด |

-VS

-VS -15V แหล่งจ่ายไฟ

-15V แหล่งจ่ายไฟ

D15 เอาต์พุตดิจิตอล 15

เอาต์พุตดิจิตอล 15 ).

).

+15V พาวเวอร์ซัพพลาย

D16

ดิจิตอลเอาท์พุต 16 (LSB)

ยับยั้ง

อินพุตสัญญาณคงที่

เวล

S1, S2, S3, S4

S1, S2, S3, S4

อินพุตสัญญาณอ้างอิงต่ำสุดofต่ำกว่า | อินพุตสัญญาณ 8 บิตที่เปิดใช้งาน พินนี้เป็นพินอินพุตลอจิกของofการควบคุม data gating หน้าที่ของมันคือการดำเนินการควบคุมสามสถานะ |

|  |

| ภายนอกบนข้อมูลเอาต์พุต 8 บิตที่ต่ำกว่าของตัวแปลง ระดับต่ำคือ | ถูกต้อง ข้อมูลเอาต์พุต 8 บิตที่ต่ำกว่าของตัวแปลงจะใช้ข้อมูล |

สถานะความต้านทาน และอุปกรณ์ไม่ได้ใช้บัสข้อมูล เปิดใช้งานและเวลาหน่วงการปล่อยคือ 600ns (สูงสุด) | สูงกว่า | อินพุตสัญญาณ 8 บิตที่เปิดใช้งาน พินนี้เป็นพินอินพุตลอจิกของ | การควบคุม data gating หน้าที่ของมันคือการดำเนินการควบคุมสามสถานะ | ภายนอกบนข้อมูลเอาต์พุต 8 บิตที่สูงกว่าของตัวแปลง ระดับต่ำ | ถูกต้อง ข้อมูลเอาท์พุต 8 บิตที่สูงกว่าของตัวแปลงจะใช้บัสข้อมูล; ที่ระดับสูง พินของข้อมูลเอาต์พุต 8 บิตที่สูงกว่าอยู่ในระดับสูง | สถานะความต้านทาน และอุปกรณ์ไม่ได้ใช้บัสข้อมูล เปิดใช้งาน | และเวลาหน่วงการปล่อยคือ 600ns (สูงสุด) | ยับยั้งไฟฟ้าสถิต |

อินพุตสัญญาณ พินนี้เป็นพินอินพุตของลอจิกควบคุม หน้าที่ของมัน | คือการส่งออกข้อมูลภายนอกไปยังตัวแปลงเพื่อให้เกิดทางเลือก | Niการควบคุมการล็อคหรือบายพาส ในระดับสูง ข้อมูลเอาท์พุตของ | ตัวแปลงเอาต์พุตโดยตรงโดยไม่ต้องสลัก ในระดับต่ำ ผลผลิต | ข้อมูลของตัวแปลงถูกล็อค ข้อมูลไม่ได้รับการอัพเดต แต่การวนซ้ำภายในไม่ได้ถูกขัดจังหวะ และการติดตามกำลังทำงานทั้งหมด | เวลา Inhibit ได้เชื่อมต่อการต้านทานการดึงขึ้นภายใน หลังจาก 600ns (สูงสุด) ล่าช้าของ | Au จากมากไปน้อยของสัญญาณคงที่ข้อมูลจะมีเสถียรภาพ (ไม่ว่า | อุปกรณ์ใช้บัสข้อมูลเช่น เมื่อใดที่มันส่งออกข้อมูลขึ้นอยู่กับในสถานะของ | และCB "ไม่ว่าง" สัญญาณเอาท์พุต สัญญาณนี้บ่งชี้ว่ารหัสไบนารี |

X

X