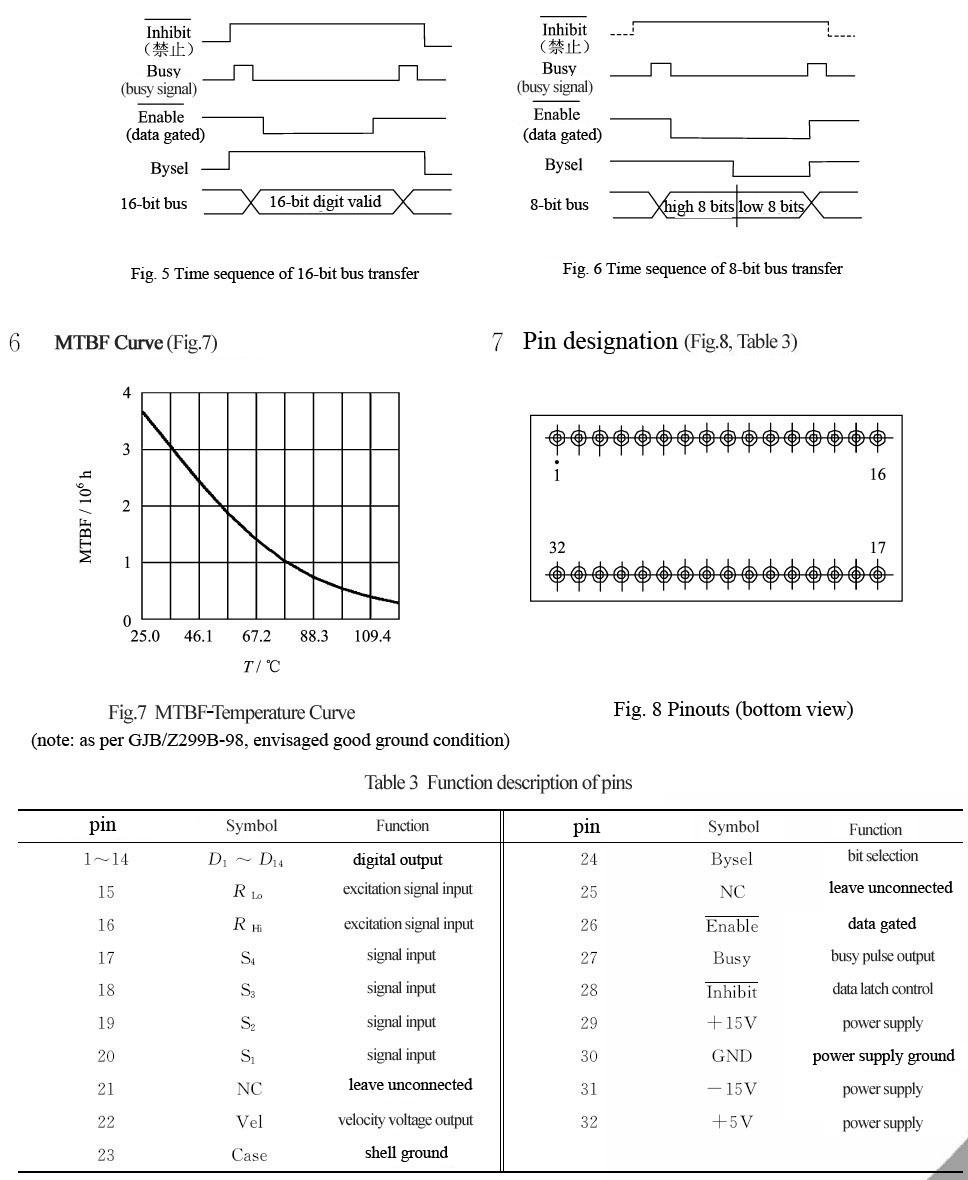

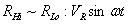

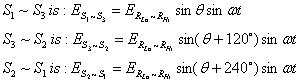

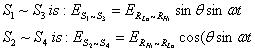

กำลังไฟในการทำงานใช้กำลังไฟ DC ±15V และ + 5V สัญญาณเอาท์พุตมีสองประเภท: ซิงโครนัสสามบรรทัดและสัญญาณอ้างอิง (ตัวแปลง SDC) หรือตัวแก้ไขสี่บรรทัดและสัญญาณอ้างอิง (ตัวแปลง RDC); เอาต์พุตใช้รหัสดิจิตอลคู่ขนานของระบบไบนารี

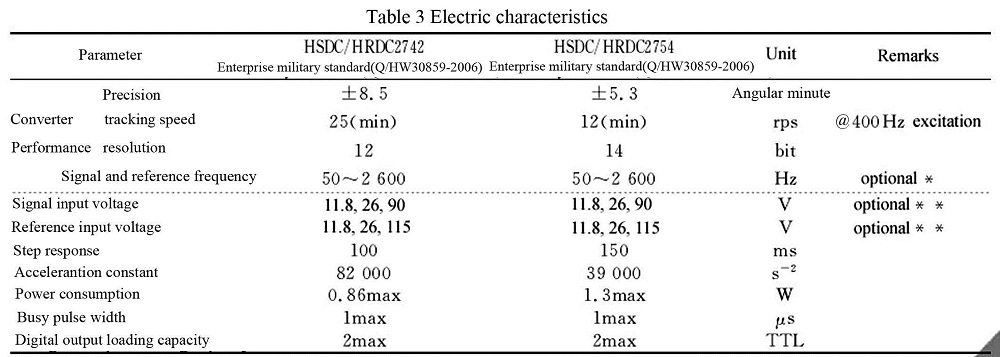

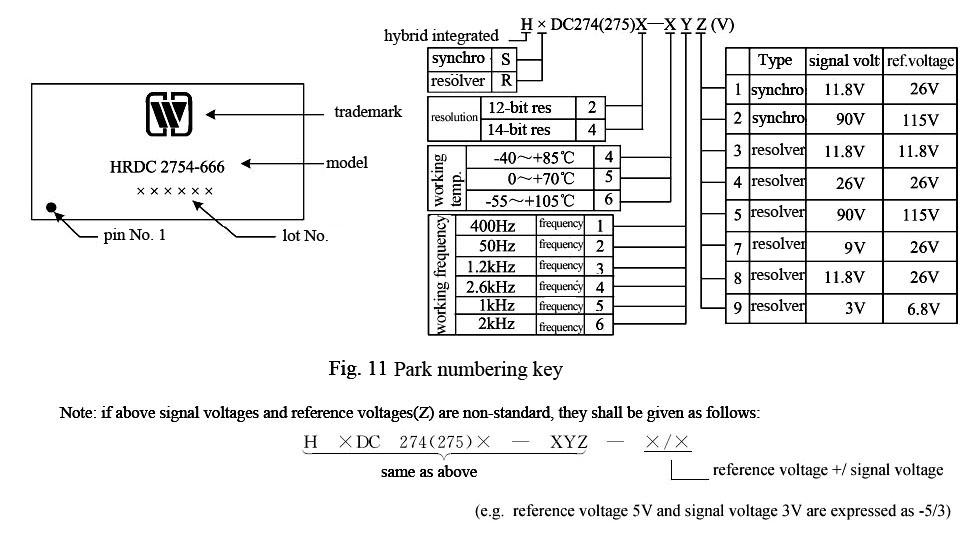

| ความละเอียด: 12 บิต 14 บิต |  |

| ความเร็วในการติดตามสูง | |

| การบูรณาการแบบไฮบริด, ตัวเรือนโลหะ | |

| เอาต์พุตสลักสามสถานะ | |

| ด้วย สัญญาณความเร็ว Vel output | |

| เข้ากันได้ไม่แน่นอนกับ AD1740 ซีรีส์ |

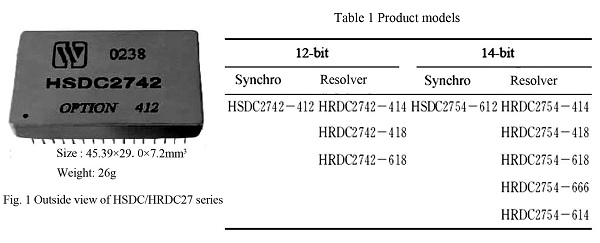

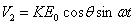

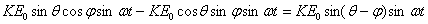

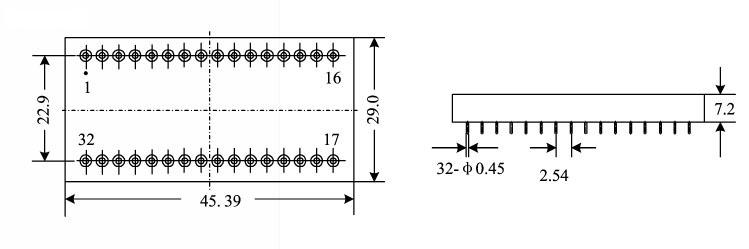

HSDC/HRDC27 ซีรีส์เป็นตัวแปลงดิจิทัลเพื่อซิงโครไนซ์หรือรีโซลเวอร์กับตัวแปลงดิจิทัลสำหรับการติดตามอย่างต่อเนื่องของลูปเซอร์โวประเภท II โดยจะสลักและส่งออกข้อมูลไบนารีธรรมชาติแบบ 12 บิตหรือ 14 บิตด้วยโลหะแบบดูอัลอินไลน์ 32 บรรทัด แพคเกจคุณลักษณะข้อดีของปริมาณขนาดเล็ก น้ำหนักเบา และความน่าเชื่อถือสูงเป็นต้น มันถูกนำไปใช้อย่างกว้างขวางในระบบควบคุมอัตโนมัติเช่นระบบเรดาร์ ระบบนำทาง ฯลฯ

กำลังไฟในการทำงานใช้กำลังไฟ DC ±15V และ + 5V สัญญาณเอาท์พุตมีสองประเภท: ซิงโครนัสสามบรรทัดและสัญญาณอ้างอิง (ตัวแปลง SDC) หรือตัวแก้ไขสี่บรรทัดและสัญญาณอ้างอิง (ตัวแปลง RDC); เอาต์พุตใช้รหัสดิจิตอลคู่ขนานของระบบไบนารี

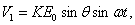

ตารางที่ 2 เงื่อนไขการจัดอันดับ และ เงื่อนไขการใช้งานที่แนะนำ

ค่าสัมบูรณ์ สูงสุด ค่านิยม | แรงดันไฟจ่าย Vs: ± 17.5V |

แรงดันลอจิก VL: +5.5V | |

ช่วงอุณหภูมิในการจัดเก็บ: -55℃~+125℃ | |

เงื่อนไขการใช้งานที่แนะนำ | แรงดันไฟจ่าย Vs: ± 5V |

แรงดันลอจิก VL: 5V | |

ค่าประสิทธิผลของแรงดันอ้างอิง VRef: ±10% ของค่าเล็กน้อย | |

ความถูกต้องของแรงดันไฟฟ้าสัญญาณ V1*: ±5% ของค่าที่ระบุ | |

ความถี่อ้างอิง f*: 50Hz~2.6kHz | |

ช่วงอุณหภูมิในการทำงาน TA: -40~+85℃,-55~+105℃ |

หมายเหตุ: * ระบุว่าปรับแต่งได้ตามความต้องการของผู้ใช้

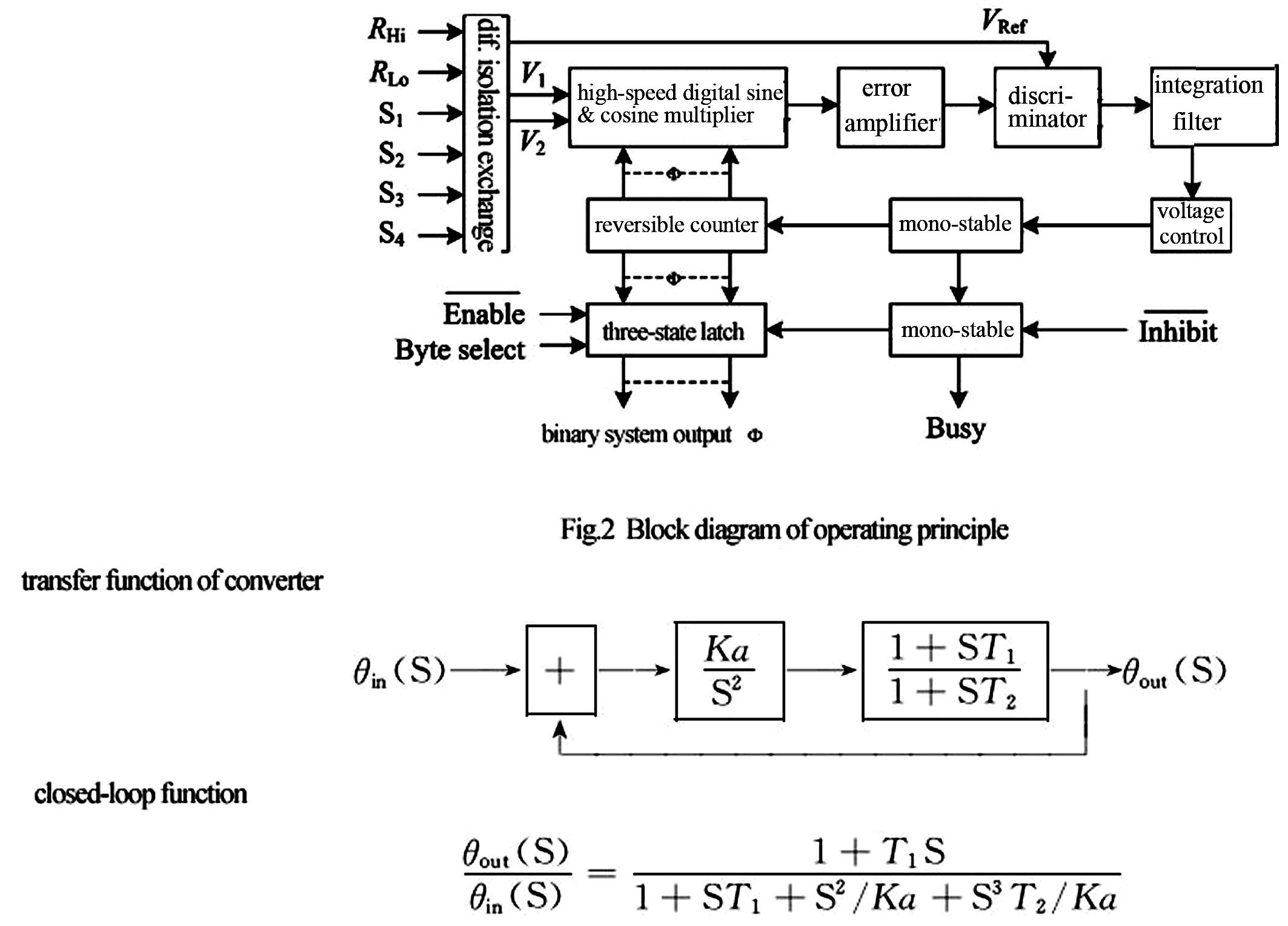

| เอาท์พุท; อ่านข้อมูล 12 บิตหรือ 14 บิต ตั้งค่า Inhibit เป็นตรรกะ “1” เหมือนกับ to |  |

| การถ่ายโอน 16 บิต) | B: ตัวแปลงเชื่อมต่อกับบัส 8 บิต, D1~D8 บิตเชื่อมต่อกับบัสข้อมูล และส่วนที่เหลือว่างเปล่า |

| |

| ยับยั้งคือ | |

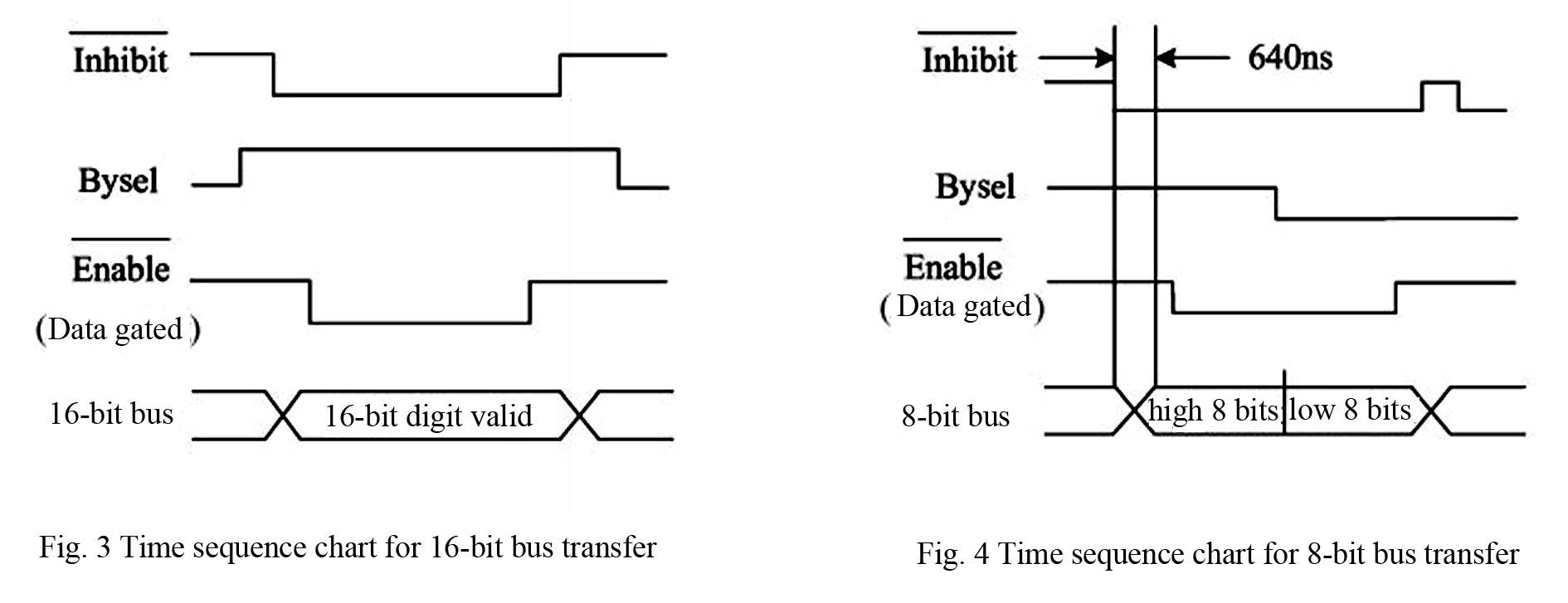

| เปิดใช้งานลอจิก "0" ข้อมูลสลักภายในตัวแปลงได้รับอนุญาตให้ | เป็นผลผลิต; ถ้า Byse1 ถูกตั้งค่าเป็นลอจิก "1" ตัวแปลงจะอ่านโดยตรง | ข้อมูล 8 บิตที่สูงกว่า ถ้า Byse1 ถูกตั้งค่าเป็นลอจิก “0” ตัวแปลงจะอ่านว่า | บิตที่เหลือจะเพิ่มศูนย์โดยอัตโนมัติสำหรับบิตที่ไม่สมบูรณ์ ตั้งค่า Inhibit data locking control (Inhibit signal) เป็นลอจิก “1” เพื่อเตรียมพร้อมสำหรับการอ่านข้อมูลถัดไปที่ถูกต้อง (ดูรูปที่ 3 และรูปที่ 4 สำหรับลำดับเวลาการถ่ายโอน 8 บิต) | (2) วิธีไม่ว่าง (การอ่านแบบอะซิงโครนัส): | ในโหมดการอ่านแบบอะซิงโครนัส Inhibit data locking control (Inhibit signal) จะถูกตั้งค่าเป็นลอจิก "1" หรือว่าง ไม่ว่าลูปภายในจะอยู่เสมอหรือไม่ | จะต้องกำหนดสถานะเสถียรหรือว่าข้อมูลที่ส่งออกถูกต้องหรือไม่ | ผ่านสภาวะสัญญาณไม่ว่างไม่ว่าง เมื่อสัญญาณ Busy อยู่ที่ระดับสูง | ระดับก็แสดงว่าข้อมูลกำลังถูกแปลงและข้อมูลที่นี้ |

| เวลาไม่เสถียรและไม่ถูกต้อง เมื่อสัญญาณ Busy อยู่ในระดับต่ำก็ | แสดงว่าการแปลงข้อมูลเสร็จสิ้นแล้ว และข้อมูลที่นี้ | Au | เวลามีเสถียรภาพและถูกต้อง เมื่อระดับสูงเกิดขึ้นใน Busy ระหว่างการอ่าน | Au | การอ่านเวลานี้ไม่ถูกต้อง ในโหมดการอ่านแบบอะซิงโครนัส ไม่ว่าง | Au | เอาต์พุตคือพัลส์เทรนของระดับ TTL ความกว้างระหว่างนั้นสัมพันธ์กับ | ความเร็วในการหมุน ในทำนองเดียวกัน ยังมีการใช้งานสองแบบ 8 บิตและ 16 บิต |

X

X